Vincent Platform consists of a number of EDA tools and IP module libraries, enabling reliable integration and verification of multiple-clock domain designs

vGenerator

A synchronization IP cores generator, offering a variety of reliable and verified synchronization solutions for different clock domain crossing types and for different system requirements

vChecker

Static Clock Domain Crossing (CDC) verification and CDC management tool, enabling efficient CDC identification, analysis, treatment and reliability grading.

vTest

Regression tests management tool, employed during design sign-offs and for multiple-mode CDC analysis

vSync Libraries

Special vSync Circuits libraries for Multiple Clock Domain design RTL and gate-level verification and ASIC or FPGA synthesis

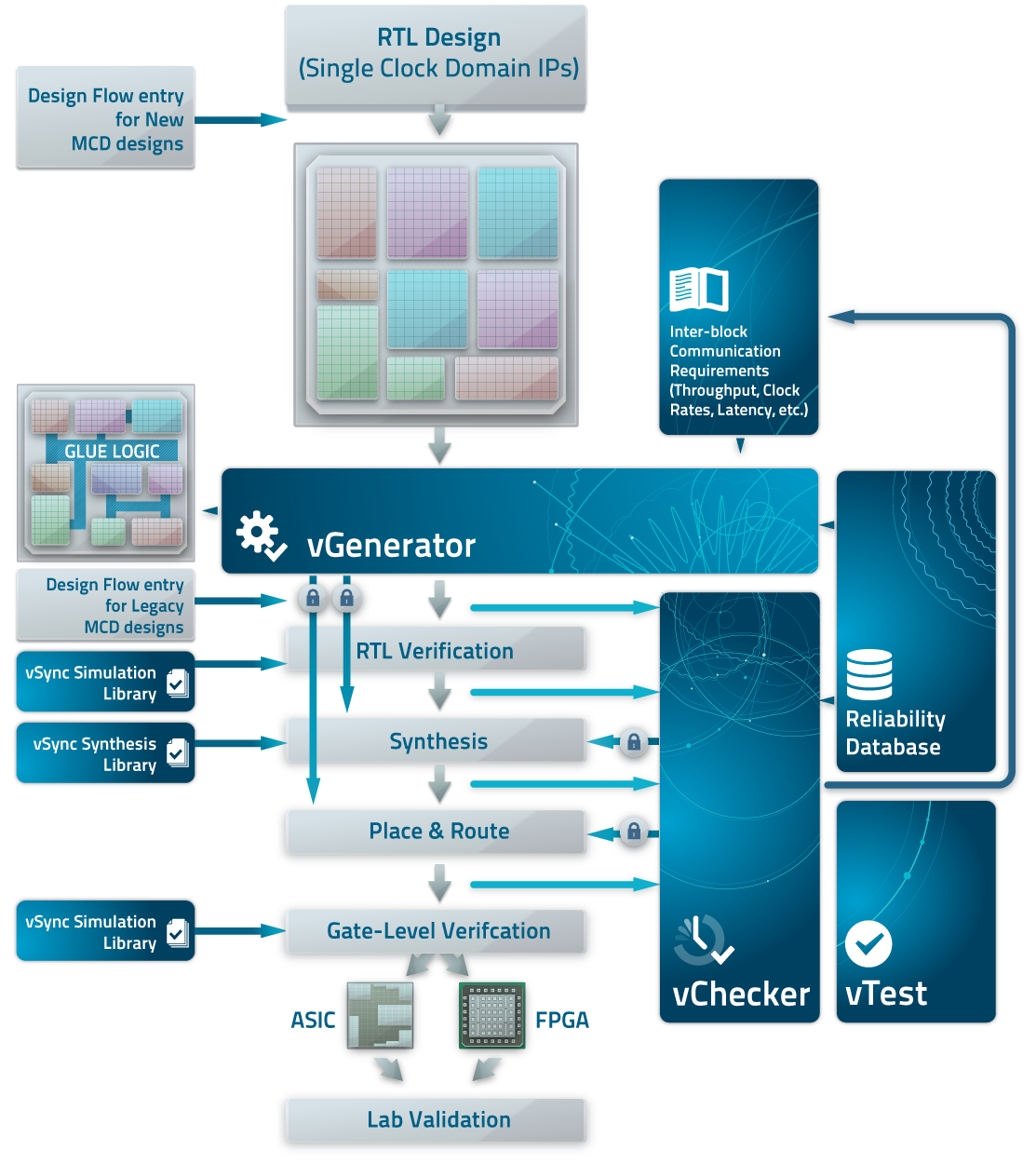

The recommended design flow with Vincent Platform is shown on the right. Vincent Platform is incorporated within a regular design flow, which consists of RTL design, RTL functional verification (simulation), synthesis, P&R and gate-level verification. The regular design flow is upgraded as follows:1

First, to reliably integrate multiple cores vGenerator tool is employed (different colored blocks in the picture on the right relate to different clock domains). The user specifies the inter-block communication requirements, including throughput, latency, buffering and clock domains. According to user requirements, vGenerator produces a glue logic (IP core), which supports the user requirements and reliably interconnects all the single clock domain blocks. In addition to the IP core RTL, vGenerator produces a number of supplemental files, including synthesis and P&R constraints (marked as locks in the picture on the right), timing constraints, reports and auxiliary information files.

vGenerator relies on a rich and highly configurable IP core library, containing different synchronization solutions. vGenerator suggests optimal solution according to user requirements. In some cases, a number of solutions are provided and the tool suggests a preferred one. The IP configuration takes into account target technology, assessing the solution reliability based on the information from the vSync Reliability Data Base (DB).

At the second stage, the design is statically analyzed by vChecker. vChecker is applied at RTL or netlist level, when the design is provided in VHDL, Verilog, System Verilog or any mix of the above. vChecker performs CDC verification, including CDC identification, classification and reliability grading. vChecker triggers vGenerator to fix the identified problems. Employing vChecker and vGenerator in a ‘find & fix’ cycle leads to a clean design. Once the design is clean, vChecker generates constraints for the entire design.

At the third stage, system-level verification is performed employing a standard functional simulator and special vSync Simulation library, which is simply linked to the simulator. The library allows emulation of system level synchronization effects, stressing the design to work under lab-like conditions. The library allows producing multiple scenarios and is controlled through external setup file, enabling emulation of different special effects.

At the fourth stage, design synthesis is performed employing vSync Synthesis library and the constraints generated by vChecker. vSync Synthesis library is tool-independent, supporting all kind of ASIC and FPGA synthesis flows. vSync IP modules contain in their code additional vendor-independent constraints. However, the constraints generated by vChecker are vendor-dependent, requiring regeneration once a target synthesis or P&R tool is changed.

At the last stage, Regression runs are performed using vSync vTest tool. The goal of the regression tests is to assure that a change, such as a bug-fix, did not introduce new bugs. Regression suite allows a convenient project management, popping up timely new problems and tracking the old ones. In addition, vTest allows automatic run of series of tests both for different designs and for different modes of a certain design. vTest tool is part of a sign-off process for each design version release.

The design flow with vSync Vincent platform supports both new and legacy designs, allowing two design entries. For new designs, the entire design integration is handled by the vGenerator, and then the rest of the flow is employed. The legacy designs are first analyzed by vChecker and are verified by functional simulation with vSync Simulation library. The discovered problems are corrected by vGenerator, and thereafter the rest of the flow is employed as for new designs.

Employing the recommended design flow enables cleaning up the CDC problems at earliest design stage, saving lab testing time as well as the integration and verification times. The reliability assessment, provided by the Vincent platform, enables verification of the events that might appear only at the customer site.

Download Product Brochure