vLinter: early rule-based design analysis and verification

Main Features

- Multiple pre-defined rule sets

STARC

RMM

DO-254

Safe Logic

- An efficient rule policy management

Per project

Per design group

Rule Customization by user

Rule import and export

Rule severity setting

- Auto-setup using FPGA/ASIC

vendor project files

Vivado

ISE

Quartus-II

Synplify

- Support of different HDL design entries

VHDL

Verilog/SV

Mixed

- Support of ASIC and FPGA flows

- Efficient violations management

Filters

Comments

Waivers

- Black-box support

- Support of different OS platforms

Windows

Linux

- Unified data base with vSync Vincent CDC

platform - HTML report

Rule policy employed

Black-box list

Violations list

Waivers list

- Qualification data-base

Ready for DO-254 tool qualification

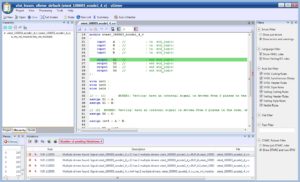

vLinter is a static analysis-based verification tool employed in early design stages for hunting design bugs related to bad coding practices. Some examples of such bugs are: unsynthesizable code, unintentional latches, undriven signals, race conditions, out of range indexing, incomplete case statements, mismatch between simulation and synthesis, etc.

RulesvLinter contains multiple rule sets that are employed to construct a customized rule policy for a project or a design group. RTL design is analyzed according to the rule policy, and all the breached rules are reported as violations for an user review.

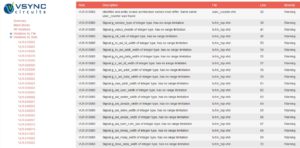

ReportvLinter allows an efficient violation report management through different violation report views. At the last stage, vLinter supports generation of comprehensive analysis reports, required for further project design reviews, qualifications and certifications.

MethodologyvLinter can catch bugs, requiring no specific test vectors and it is very effective when employed pre-simulation, reducing the number of simulation cycles needed to cover a functionality of a RTL module. The recommended design flow suggests employing vLinter before any functional verification.

FlowsvLinter supports both ASIC and FPGA design flows, allows easy and fast setup by directly loading in project files of leading ASIC and FPGA vendor synthesis tools.

CDCvLinter is compatible with vSync Vincent CDC platform, allowing an immediate switch to CDC (Clock Domain Crossing) analysis after reviewing linter violations.

SupportvLinter supports all VHDL and Verilog/System Verilog standards, including mixed-language design. In addition, the tool handles efficiently partial design, having internal black boxes. vLinter supports both Windows and Linux platforms.

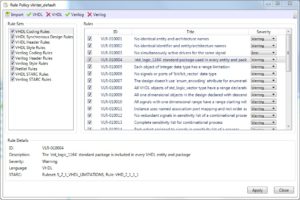

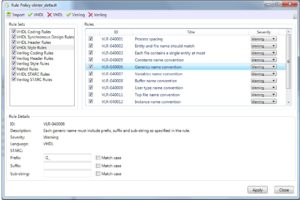

Rule Policy Settings

The user can activate / deactivate the rules out of the rule list, creating a user-defined rule policy. The rule policy is stored in a special rule policy file, which can be then exported / imported to / from other design projects. The rule policy file name is noted in all vLinter reports. vLinter rules having matching STARC rules, include a special reference to STARC rule set and rule number.

Violation Management

The user can decide to disregard some reported violations. This decision can be managed through Waive and Comment vLinter interface. The user marks

the violation as waived and writes a comment describing the reason for this decision. The waived violations can be filtered out from the report and appear as a special section in a final HTML report of the project.

vLinter allows fast design analysis, enabling clear up of simple and complex bugs prior to functional simulation. The tool can be employed to enforce certain design methodology for design group by customization of required Rule Policy.

Download Product Brochure