vAXIom Platform: Flexible Slave and Master modules for integration over AXI Interconnect, accompanied with simulation and synthesis environments, enabling customized, functional from day one system infrastructure for firmware and SW development

vAXI-Slave and vAXI-Master IP modules are peripheral slave and master interface components on AXI4 interconnect. vAXI modules facilitate fast and smooth integration of user hardware modules with AXI interconnect, possibly connected on the other side to embedded processors of different vendors or other AXI masters, e.g. Xilinx Zynq PS, uBlaze, Altera SoC HPS, Nios-II or ARM. vAXI modules support memory mapped AXI4 and AXI4-lite protocols. vAXI supports different types of user ports, including a special interface for an off-chip communication, enabling AXI protocol extension to other on-board chips. Generated with a ready-to-use synthesis and simulation environments, vAXI modules enable swift ramp up of System-on-Chip designs.

vAXI solutions facilitate reliable and fast SW/HW integration, providing a standard AXI4 connection on one side, and multiple ‘user port’ connections on the other side, when the user ports support a variety of standard interface protocols. vAXI is optimized for required AXI/user port clock relationships, providing low-area, low-latency, reliable and fully back-pressed communication

Main Features

- AXI4 and AXI4-Lite protocols

- Single and burst accesses over AXI4 interconnect

- Unlimited user ports with different clocking schemes

- Different interface types for each user port

- Different interface types for each user port

+ Memory

+ Input/output Buffers

+ SBUS (off-chip)

- Different interface protocols

+ Wishbone

+ Pulse

- Separate configuration (data width, buffer depth) of each user port

- Optional double buffer for all types of user interfaces

- Special interfaces (SBUS) for off-chip communication

- Low area through internal resource sharing

- Synthesizable both for FPGA and ASIC

- Provided with an easy to use user interface facilitating fast configuration and generation

- Automatically recognized by leading vendor tools, when connecting to AXI4 interconnect

- Automatically triggers vendor tools for required vendor IPs (e.g. memories) and synthesis and verification environment generations

4 Easy Stages to Setup up your SoC with vAXIom Platform

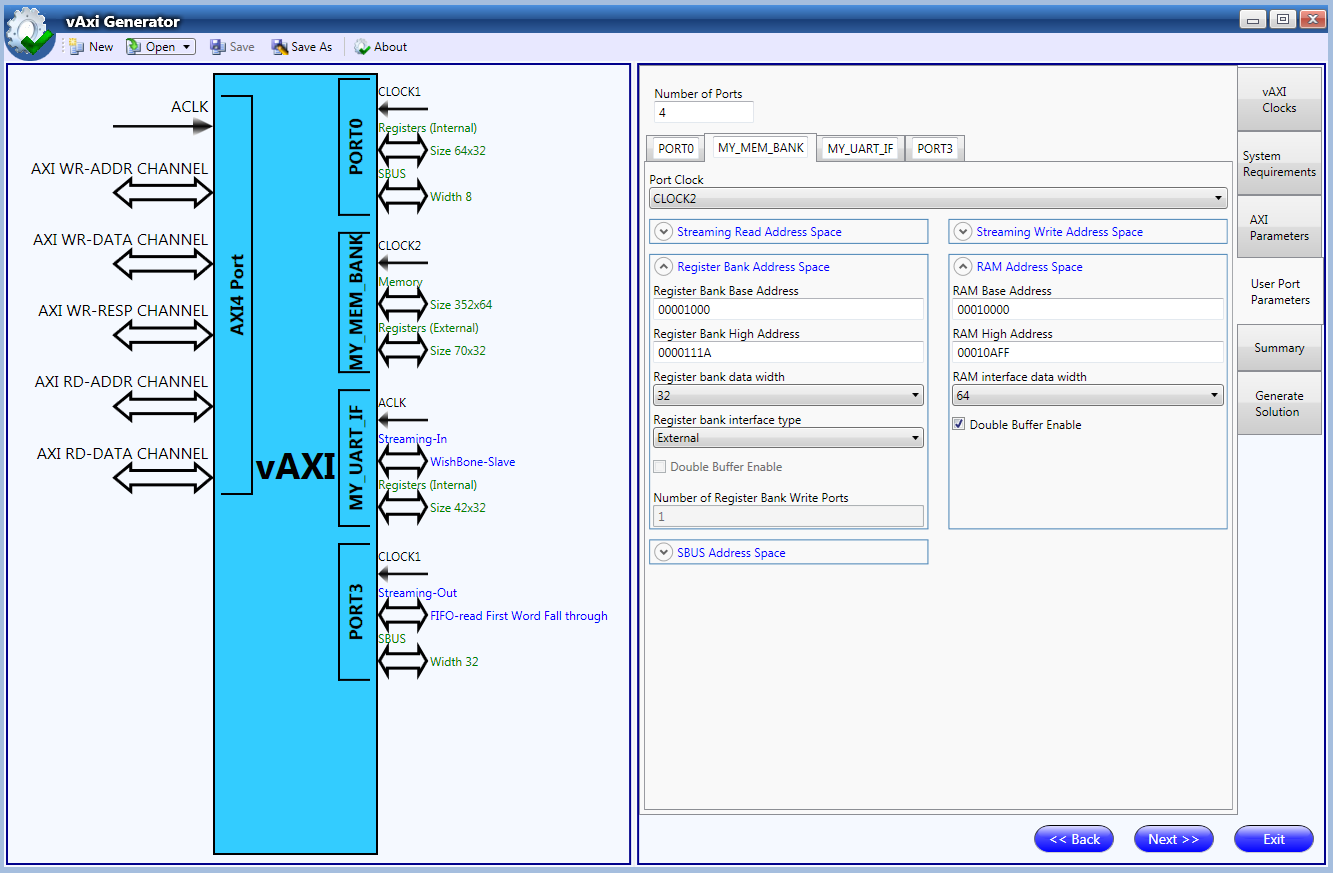

vAXI is customized and generated using an easy-to-use graphical user interface (GUI), setting up a targeted AXI protocol, user ports and interfaces, addresses and target device. The customized vAXI module can be modified at any stage of the following design process using the same GUI.

vAXI module is generated along with sample environments for synthesis and simulation. A sample top module is generated, containing the customized vAXI module connected to AXI interconnect. The sample top module contains also ARM system and USB/JTAG module connected to the AXI interconnect. The generated simulation environment exemplifies accessing all the customized interfaces in simulation, and serves as a start point for the development of verification environment for entire design, supporting gradual add-on of user functional modules to the top module.

The automatically generated at the previous stage sample top module is ready to use (synthesizable) without any modification. The designer can, however, modify the top module by connecting custom firmware modules to AXI user ports and by connecting additional modules directly to AXI interconnect (e.g. DDR3 controller). The sample top module requires setting up the pin connections for clock and reset pons only. Once the modifications are done, the design is compiled and burnt into the target device.

At the last stage, the address space of vAXI interfaces (in general of entire AXI interconnect) can be accessed through the JTAG/USB connection. vAXI software automatically generates a sample command script that performs write and read transactions, according to vAXI user configuration. The same operations can be done from ARM, when the automatically generated script can serve as a BIT. Once the communication is set, the user can continue building on the generated infrastructure both firmware on FPGA and software on ARM.

Employing vAXIom Platform facilitates a significant area minimization through resource sharing, flexibility, porting abilities and simplicity. vAXIom Platform enables a working customized SoC from day one, allowing a concurrent development of project firmware and software.Download Product Brochure

Setting up Xilinx Zynq with vAXIom platform

Setting up Altera SoC with vAXIom platform